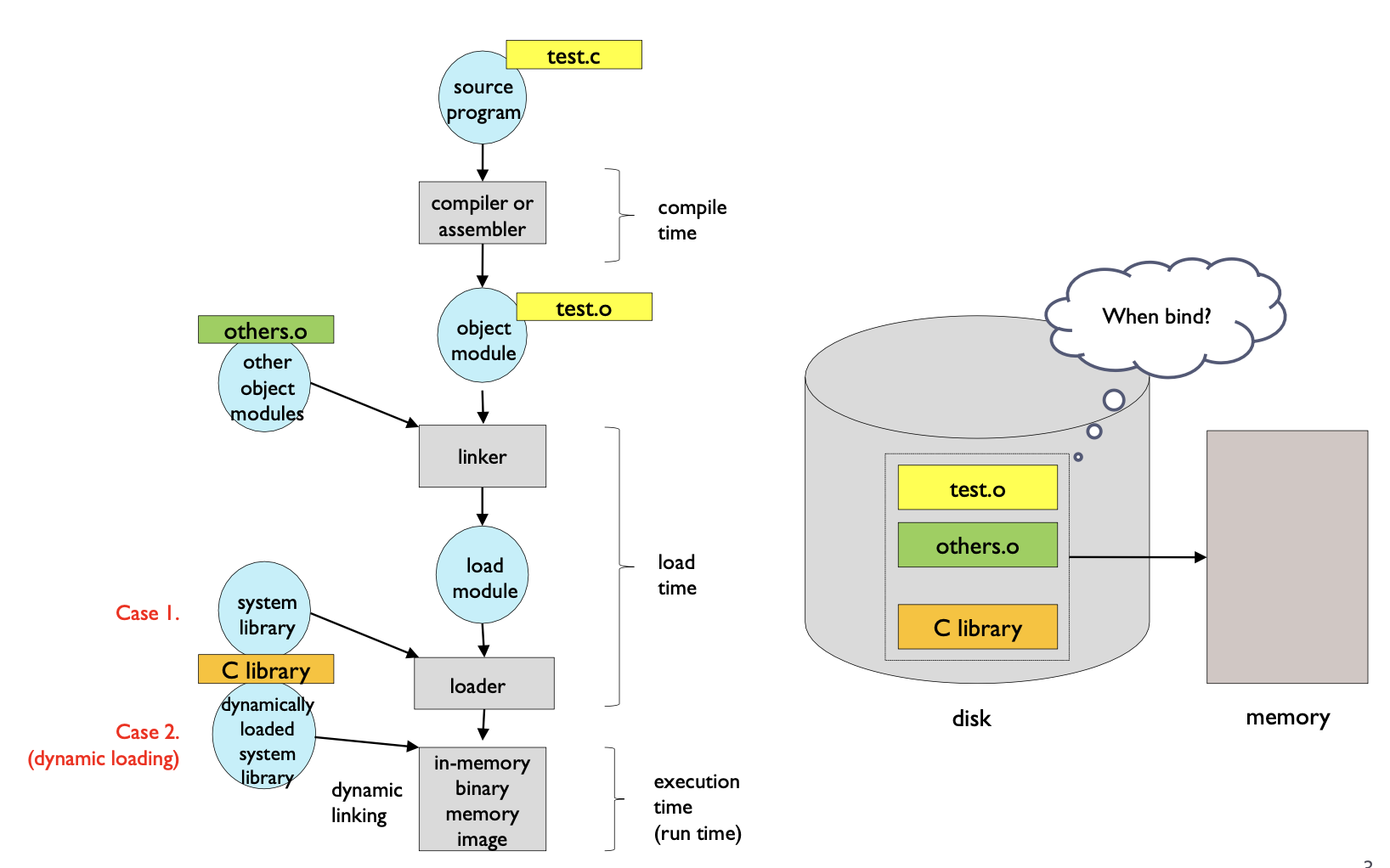

Multistep Processing of a User Program

- source program(test.c)가 compiler나 assembler에 의해 object module(test.o) 파일로 컴파일 됨(컴파일 시간)

- linker가 다른 object module과 linking 해줌

- loader가 모듈과 system library를 load함 (2, 3 과정을 load time이라고 함)

- loader에 의해 메모리에 올라온 프로세스가(실행시간에) dynamically loaded system library에서 불러온다.

(Windows의 경우 프로세스에서 DLL 파일을 실행시킨 후 프로세스로 복귀함)

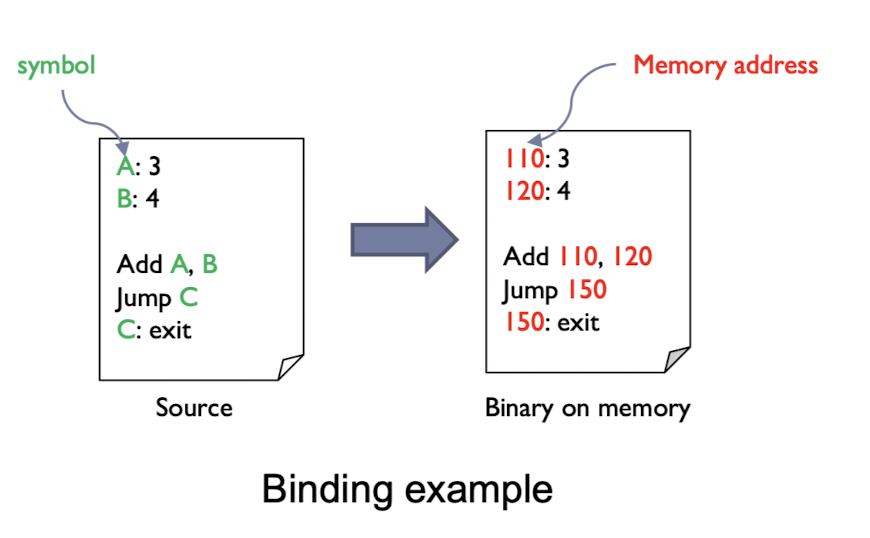

Address binding

- 프로그램 명령어와 데이터를 물리 메모리 주소에 연결하는 과정

- 명령어나 데이터에 접근할 때 주소를 이용하기 때문

- Address binding은 다음 3가지 단계에서 발생할 수 있음

- Compile time binding

- Load time binding

- Execution time binding

Compile time binding

- 만약 프로그램이 메모리에 적재되는 위치를 컴파일 시간에 알고 있다면, absolute address(절대 주소)를 가진 absolute code(절대 코드)가 생성된다

- 만약 시작 주소가 변경된다면(프로그램이 적재되는 메모리 상의 위치가 변경된다면), 반드시 코드 recompile 해야 함

Load time binding

- 만약 프로그램이 메모리에 적재되는 위치를 컴파일 시간에 알지 못한다면, relative address(상대 주소)를 가진 relocatable code(재배치 가능한 코드)가 생성된다

- 프로그램이 메모리에 적재될 때, binding이 일어남

- 프로그램의 start location(적재 위치)가 바뀌더라도, recompile 할 필요가 없다.

Execution time binding

- runtime까지 binding이 지연됨

- CPU가 주소를 생성하면(명령어나 데이터를 참조하기 위해 주소를 요청하는 경우), binding이 일어남

- 컴파일 할 때 상대주소로 변환되고, 메모리에 적재 될 때도 절대주소가 아닌 상대 주소로 적재가 됨

- CPU가 요청한 주소로 접근하기 위해서는 MMU라는 하드웨어의 도움을 통해 address mapping이 일어남

- 대부분 OS가 이 방법을 사용함

정리하자면 절대주소(컴파일 시간, disk에 절대 주소가 저장됨), 상대주소(load time), Runtime Binding(메모리에도 상대주소 상태로 적재)

그리고 아래에 논리 주소가 있음

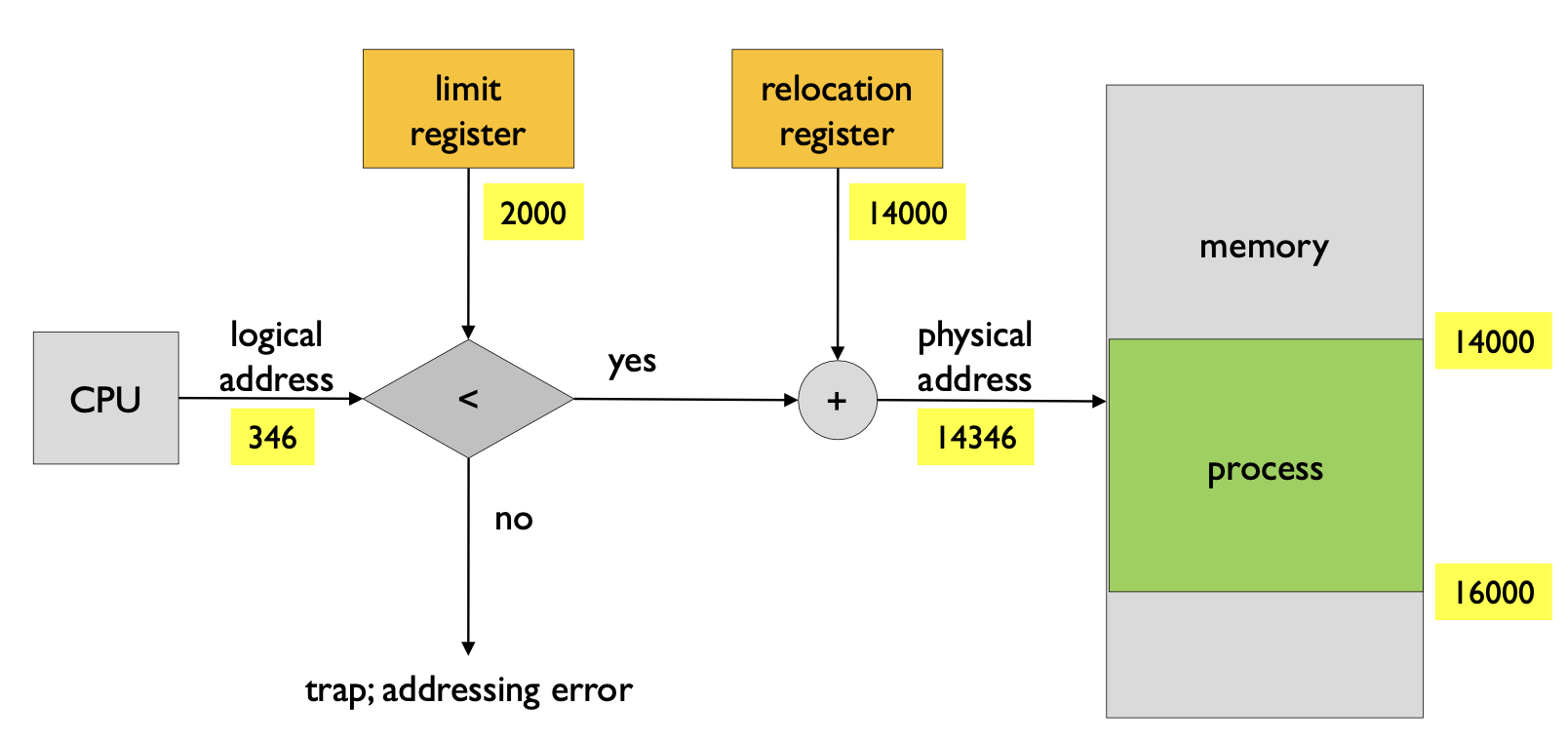

Memory Management Unit

- Logical address(논리 주소)

- CPU에 의해 생성되는 주소

- virtual address(가상 주소)라고도 함

- Physical address(물리 주소)

- 메모리 유닛에 의해 보여지는 주소

- MMU

- 논리 주소를 물리 주소로 매핑해주는 하드웨어

- Simple MMU scheme

- relocation register(재배치 레지스터)에 있는 값이 CPU에 의해 생성된 모든 주소에 더해짐

- Program과 CPU

- 논리 주소만을 다루고, 물리 주소를 절대 알지 못함

Dynamic Loading

- Routine(루틴, 프로시저나 함수로 이해하자)이 호출될 때 까지 load X

- 메모리 주소공간 활용을 효율적으로 할 수 있음

- 사용되지 않는 루틴은 절대 load X

- 많은 양의 error handling code가 필요할 때 유용하다

- Error는 자주 발생하지 않기 때문

- Load 할 때 마다 매번 동일한 address가 비어있지 않는다

- 어디든지 load 될 수 있기 때문에 dynamic linking이 필요하다

Dynamic Linking

Dynamic linking

- Linking이 execution time까지 연기된다

Shared library

- library를 필요로 하는 모든 프로세스에 대해 메모리에 하나의 복사본만 있어도 충분하다

Swapping

Swapping

- 프로세스는 일시적으로 메모리에서 백업 저장소로 스왑된 다음, 나중에 메모리로 가져올 수 있다

Backing store

- 모든 이미지를 수용할 만큼 빠르고 크다

- ex) disks

Contiguous Allocation

- 메인 메모리는 보통 두 파티션으로 나눠진다

- 하나는 OS로

- 나머지 하나는 user process로

- 메모리 매핑과 보호

- 재배치 레지스터(Relocation registers)는 user process를 보호하기 위해 사용됨

- Limit register는 논리 주소의 범위를 가지고 있음

- 각 논리 주소는 limit register 보다 작아야 함

- (Relocation register + logical address) < (Relocation register + limit register : user process 범위)이므로, 파티션을 넘어서 접근하지 못한다

- MMU는 동적으로 논리주소를 매핑함

- 재배치 레지스터의 값을 더함으로써 매핑

- Hardware는 연속적인 메모리 할당을 지원함

Memory allocation

메모리 공간은 크게 운영체제를 위한 공간과 프로세스를 위한 공간으로 나눌 수 있습니다.

운영체제는 시스템의 전원이 꺼질 때까지 메모리의 일정 부분을 계속 차지하게 되지만, 프로세스들은 생성과 종료에 따라 메모리 공간을 차지하기도 하고 반납하기도 합니다.

그림 (a)와 같이, 메모리의 윗부분에 운영체제가 있고, 그 아래에 프로세스 1, 프로세스 2, 프로세스 3가 있다고 가정하겠습니다.

프로세스 2가 종료되면 사용중인 메모리 공간을 반납하게 되어 그림 (b)처럼 바뀝니다.

그런 다음, 프로세스 4가 생성되면 그림 (c)와 같은 모양이 되고, 여기에서 프로세스 1이 종료되면 그림 (d)처럼 됩니다.

즉, 프로세스의 생성과 종료에 따라 다양한 크기의 홀(hole)이 메모리 곳곳에 생기는데요.

프로그램은 메모리에 적재될 때 전체 이미지를 수용할 수 있는 홀을 찾아 메모리 공간을 할당해야 할 것입니다.

따라서, 운영체제는 메모리의 어떤 공간을 할당하였는지, 또 어떤 공간이 사용되지 않는지를 지속적으로 관리해야 합니다.

- Hole (가용할 수 있는 큰 블록 메모리)

- 메모리 상에 다양한 크기의 hole이 흩어져서 존재한다

- process가 생성되면

- 수용할 수 있을만큼 충분히 큰 hole에 메모리가 할당된다

- OS는 다음과 관련된 정보를 가지고 있음

- allocated partitions

- free partitions(hole)

Dynamic Storage-Allocation Problem

프로그램을 메모리로 적재할 때, 다양한 홀 중 어디에 할당하는 것이 좋을까?

P2 / P5 / P7 프로세스에 대한 공간이 할당되어 있고, 나머지 공간은 반납되었거나 한 번도 사용하지 않은 공간. 즉 가용 공간임

운영체제는 가용 공간을 관리 하기 위한 정보를 유지하는데요.

이 예제에서는 100번지부터 140번지까지, 160번지부터 190번지까지, 230번지부터 250번지까지, 그리고 320번부터 400번까지가 가용 공간입니다.

이러한 상황에서 프로세스 8을 생성하여 프로그램을 적재하기 위해 25만큼의 메모리 공간이 필요하다고 가정해 보겠습니다.

이를 수용할 수 있는 가용 공간이 여러 개가 있는데요.

먼저, 최초 적합(first fit) 기법은 프로그램 이미지를 수용할 수 있는 가용 공간 중 첫 번째에 할당하는 방법입니다.

이 예제에서는 100번지부터 시작하는 가용 공간의 크기가 40이므로 이 프로그램을 수용할 수 있고, 따라서 최초 적합 기법에 따르면 이 공간을 할당해 줍니다.

두 번째는 최적 적합(best fit) 기법으로, 프로그램 이미지를 수용할 수 있는 가용 공간 중 가장 작은 것을 할당하는 방법입니다.

이 예제에서는 160번지부터 시작하는 가용 공간이, 수용 가능한 것 중에서 가장 작기 때문에 여기에 할당합니다.

세 번째는 최악 적합(worst fit)으로, 가장 큰 가용 공간을 할당해 주는 기법입니다.

여기에서는 320번지부터 시작하는 가용 공간의 크기가 가장 크므로 여기에 할당하게 되겠지요.

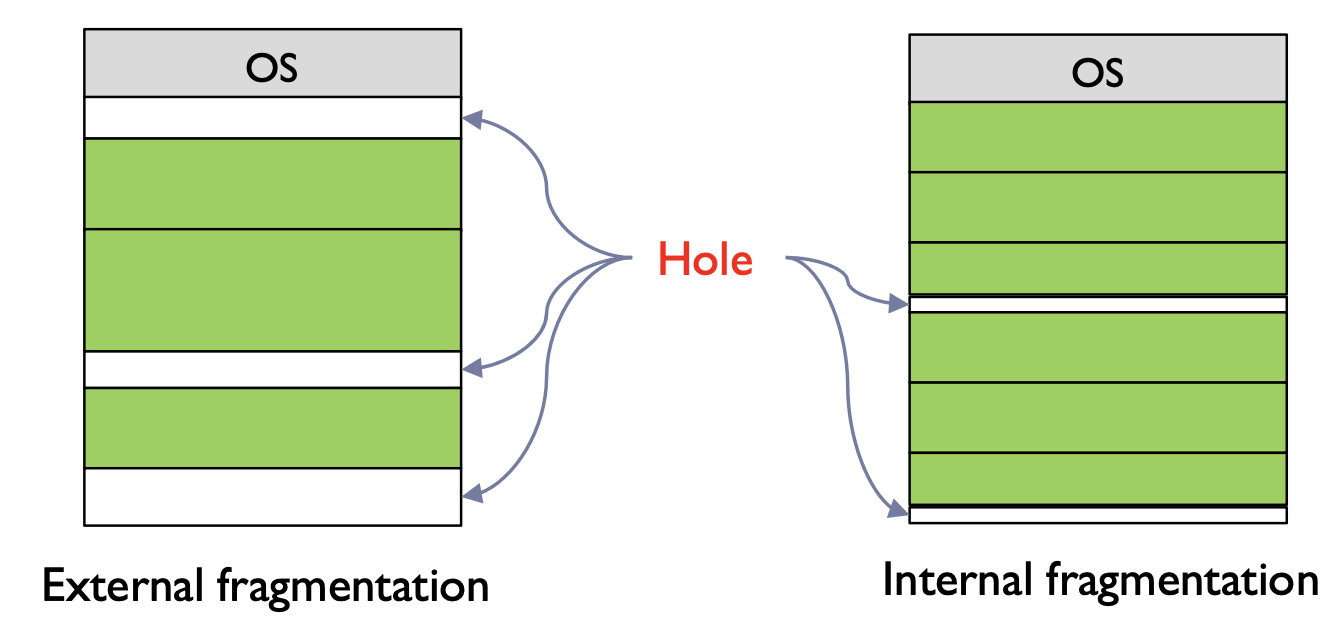

External Fragmentation(외부 단편화)

- 요청을 만족하기 위한 가용 공간이 존재하지만, 연속적이지 않음

- compactation(압축)으로 줄일 수 있음

- 모든 가용 공간을 하나의 큰 block에 모은다

Internal Fragmentation(내부 단편화)

외부 단편화 문제를 완화하기 위해 메모리를 고정된 크기로 분할하여 프로그램을 적재하는 방법

- 할당된 메모리가 요청된 메모리보다 약간 클 수 있다

- 크기 차이로 인해 파티션 내부에 남는 공간이 생길 수 있지만, 사용되지 않는다

Paging

프로그램 이미지를 통째로 메모리에 적재하는 것은 외부 단편화를 발생시키는 등 메모리 공간을 관리하기 어렵게 만드는데요.

그러한 이유로, 최근의 많은 운영체제는 페이징 기법을 사용하고 있습니다.

페이징 기법은 말 그대로 메모리를 페이지 단위로 관리하겠다는 것인데요.

먼저 메모리를 페이지 프레임이라는 고정된 크기로 나누고, 프로그램 이미지 또한 페이지라는 고정된 크기로 나눕니다.

마치 사진을 액자에 끼우듯 페이지를 페이지 프레임으로 적재하는 방식이지요.

따라서 페이지와 페이지 프레임 크기는 같아야 하고, 일반적으로 512바이트에서 8킬로바이트 사이입니다.

페이징 기법에서는 프로그램 이미지를 한꺼번에 통째로 메모리로 적재하지 않습니다.

프로그램 이미지는 그대로 디스크에 있고, 프로그램이 시작할 때 첫 번째 페이지만 메모리로 적재합니다.

나머지 페이지들은 필요할 때 그때그때 올리면 그만입니다.

따라서 프로그램의 페이지들은 각자 메모리에 있을 수도 있고, 디스크에 있을 수도 있습니다.

또한 페이지들은 연속적으로 적재될 필요없이 메모리의 아무 위치에나 적재될 수 있는데요.

이는 MMU의 일을 더 어렵게 만듭니다.

즉, 논리 주소를 물리 주소로 바꾸기 위해서는 각 페이지가 어느 페이지 프레임에 적재되어 있는지를 알아야 하는데요.

이러한 정보는 페이지 테이블에 기록됩니다.

- 메모리와 (프로그램)이미지를 고정된 사이즈로 각각 나누는 것

- page frame과 page

- 사이즈는 2의 거듭제곱으로, 512B와 8KB 사이

- 전체 프로그램 이미지는 디스크에 있다

- 프로그램이 시작할 때, 첫 번째 페이지 메모리에 적재된다

- 나머지 페이지들은 필요할 때 메모리에 적재된다

- 프로그램의 특정 페이지 X는

- 이미 메모리에 있는 page frame Y에 적재되었거나

- 적재되기 전이라, 디스크에 있다

- 페이지는 메모리의 아무 위치에나 적재될 수 있다

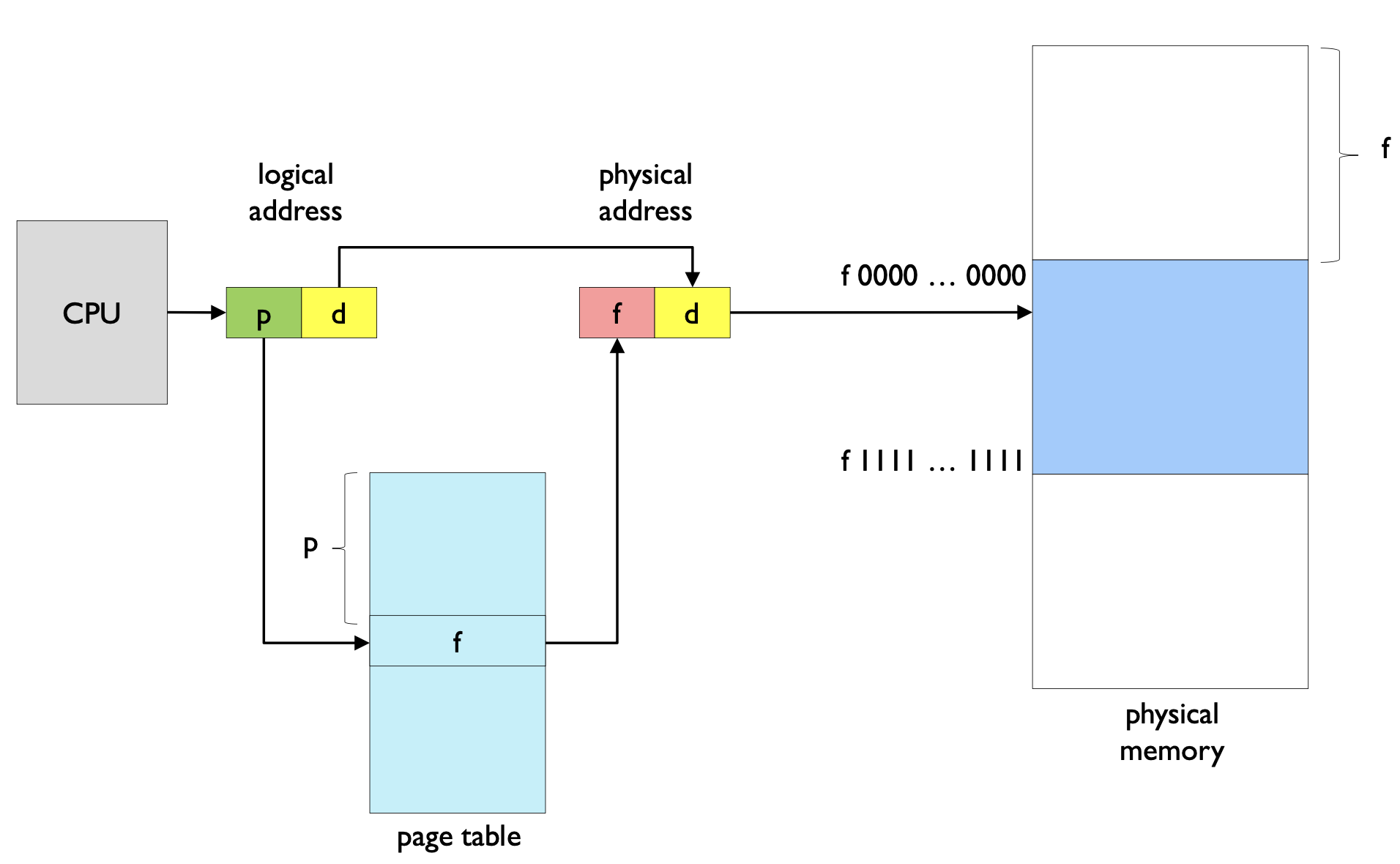

- CPU가 주소를 제공할 때 마다 MMU는 page table을 찾는다

- 논리 주소를 물리 주소로 변한하기 위해

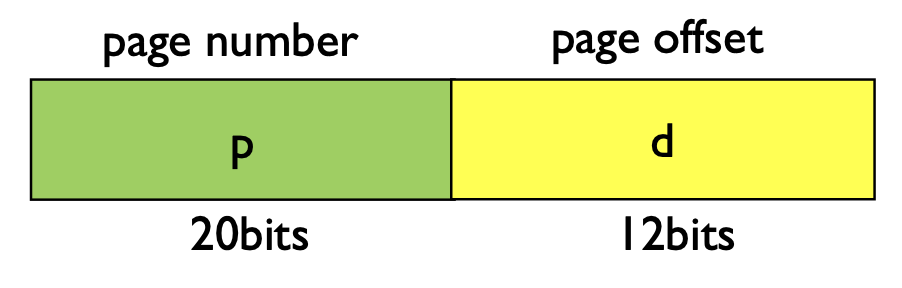

주소 변환

- CPU에 의해 생성된 논리 주소는 두가지 부분으로 나눠진다

- 예를 들어 주소의 길이가 32이고, 페이지의 크기가 4KB라고 해보자

- Page number(p)

- 페이지 테이블에서 index로 사용된다

- 인덱스가 가리키는 엔트리에는 해당 페이지가 물리적 메모리에 적재되어 있는 페이지 프레임의 시작주소(base address)가 들어 있다.

- Page offset(d)

- 물리적 메모리 주소를 정의하기 위해 시작주소와 결합한다

- 위 예시에서는 하위 12비트의 페이지 오프셋을 더해서 물리 메모리 주소를 얻어냅니다.

- 페이지 단위로 메모리에 적재하기 때문에 논리주소를 물리주소로 변환하더라도 페이지 내의 오프셋은 변하지 않음

Page number를 페이지 테이블과 비교해서 시작 주소를 얻고, Page offset과 시작 주소를 더해서 물리 주소를 얻는다

Shared pages

페이징 기법의 또 다른 장점은 코드를 쉽게 공유할 수 있다는 점입니다.

예를 들어 세 개의 문서 편집기를 실행하여 각각 다른 파일들을 작성한다고 가정해 보겠습니다.

개념적으로는 문서 편집기의 코드를 메모리에 세 카피 두어야겠지만, 메모리에 한 카피만 두고 세 프로세스가 공유하는 것이 효율적일 것입니다.

그림처럼 세 개의 프로세스들은 페이지 테이블을 통해 코드를 쉽게 공유할 수 있습니다.

각 프로세스들은 데이터 페이지만 각각 다른 메모리 공간에 적재해 두고, 코드 페이지들은 서로 공유하고 있는데요.

즉, 세 개의 코드 페이지들이 페이지 프레임 번호 3, 4, 6에 각각 적재되어 있고, 각 프로세스들은 페이지 테이블을 통해 이들을 접근하고 있음을 알 수 있습니다.

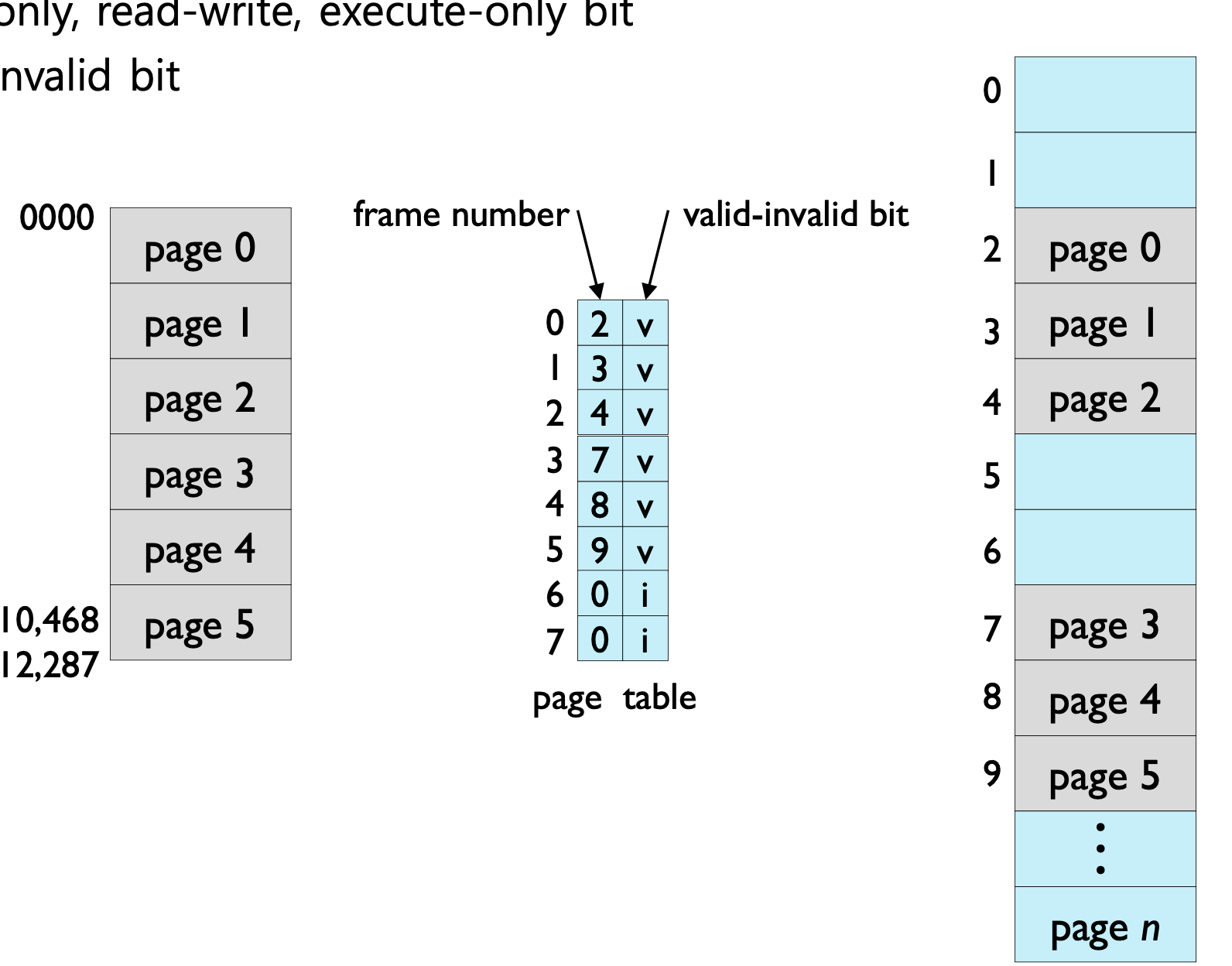

Memory protection is implemented

- 각 프레임에 protection bits를 연결

- Read-only, read-write, execute-only bit

- Valid-invalid bit

페이징 장점

- 물리적 메모리보다 큰 메모리 공간을 제공합니다.

- 32비트 프로세서라면 4GB의 논리 주소 공간이 가능하다.

- 요구 페이징(demand paging) 지원

- 메모리 배치 정책이 필요하지 않습니다.

- 페이지 공유 제공

- 메모리 공간을 서로 보호합니다.

페이징 단점

- 시간적인 오버헤드

- 페이지 테이블 또한 메모리로 적재되어야 하므로, 메모리에 적재된 코드나 데이터를 접근하기 위해 페이지 테이블을 추가로 접근해야 하는 시간적인 오버헤드가 존재합니다.

- TLB(Translation Look-aside Buffer) 로 완화

- 공간적인 오버헤드

- 페이지 테이블을 저장하기 위한 공간이 커질 수 있다는 점

- Multi-level page table, hashed page table, inverted page table

페이지 테이블의 구현

- 페이지 테이블은 메인 메모리에 보관됩니다.

- 페이지 테이블 기본 레지스터(Page-Table Base Register, PTBR)는 페이지 테이블을 가리킵니다.

- 모든 데이터/명령어 액세스에는 두 번의 메모리 액세스가 필요합니다.

- 하나는 페이지 테이블용이고 다른 하나는 데이터/명령어용입니다.

- 두 번의 메모리 접근 문제는 해결될 수 있습니다

- TLB(Translation Look-aside Buffer)를 사용합니다.

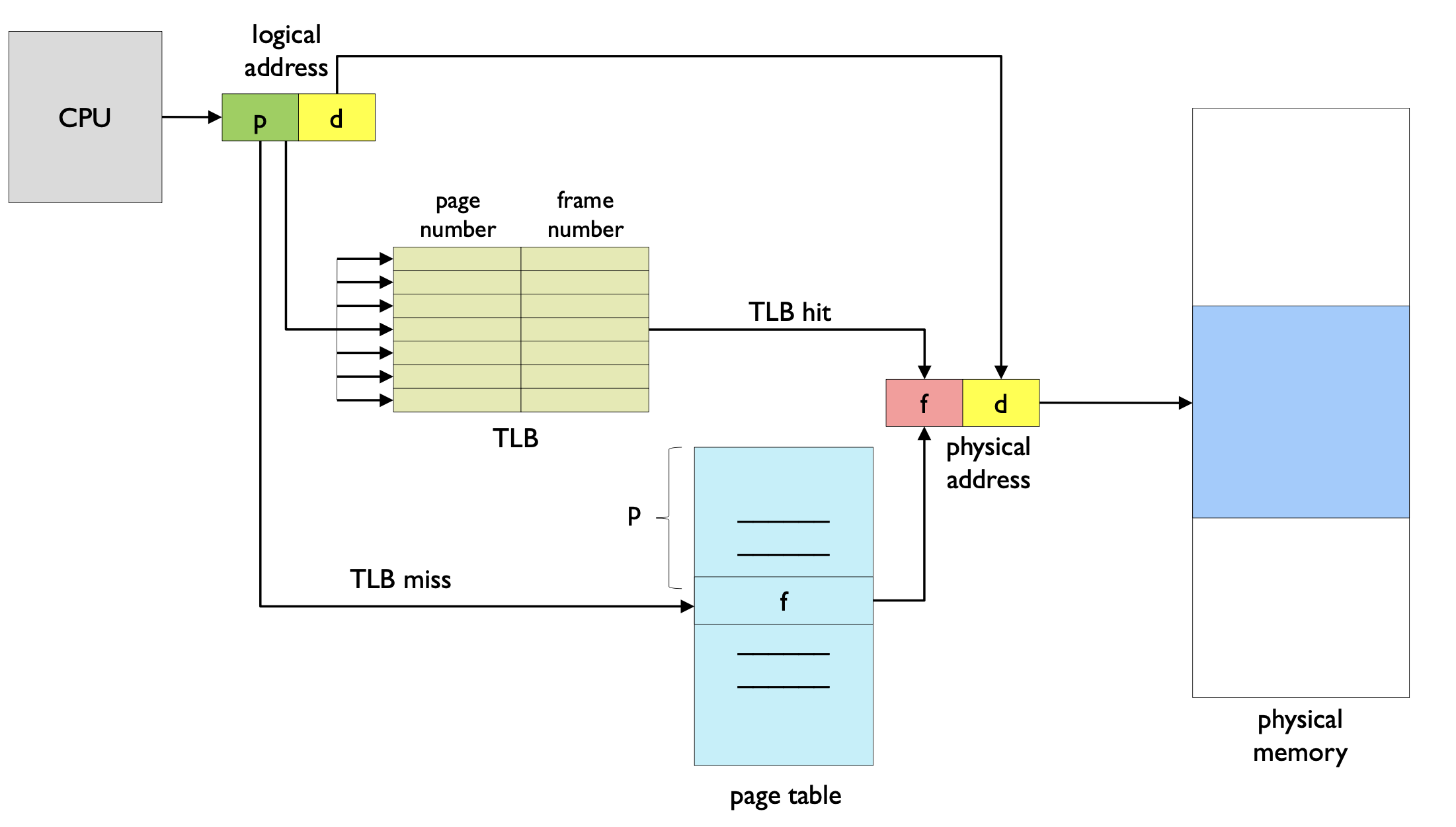

TLB를 사용한 paging

그림은 TLB가 사용된 페이징 기법의 구조를 보여줍니다.

CPU가 요청한 논리 주소를 페이지 테이블을 통해 바로 물리 주소로 변환하지 않고, 먼저 TLB에 저장된 정보를 살펴봅니다.

TLB는 Translation Lookaside Buffer (트렌스레이션 룩어사이드 버퍼)의 약자로, 자주 변환되는 주소 정보를 담고 있는 특수한 하드웨어 캐쉬입니다.

즉, CPU가 요청한 논리 주소에 대한 변환 정보가 TLB내에 있는지 먼저 살펴보고,

변환 정보가 있으면 페이지 테이블을 참조할 필요없이 바로 물리 주소로 변환하고,

변환 정보가 없으면 페이지 테이블을 참조하여 물리 주소로 변환합니다.

하지만 TLB에는 모든 페이지 번호에 대한 정보를 가지고 있는 것이 아니므로, CPU가 요청한 페이지 번호를 찾기 위해 TLB의 모든 엔트리를 탐색해야 합니다.

이는 동시에 모든 엔트리들을 탐색할 수 있는 하드웨어의 도움을 통해 일반적으로 해결합니다.

유효 접근 시간(Effective Access Time)

- TLB lookup time: ε

- Memory access time: 1

- Hit ratio: α

- Percentage that is found in TLB.

- Effective Access Time = (1 + ε) α + (2 + ε)(1 – α)= 2 + ε– α

페이지 테이블을 저장하려면 추가 메모리 공간이 필요합니다.

프로그램이 큰 주소 공간을 가지고 있다.

- 32비트 주소를 사용한다면,

- 4GB 크기의 프로그램을 처리할 수 있습니다.

- 100만 개의 페이지 테이블 항목 (페이지 크기가 4KB인 경우)

- 4MB 페이지 테이블 필요 (entry 크기가 4B인 경우, 일반적으로 4바이트임)

페이지 테이블은 프로세스별 자료 구조입니다.

- 페이지 테이블을 저장하려면 4MB * N(프로세스 수)이 필요합니다.

Page Table의 구조

- Hierarchical Page Table

- Two level page table scheme(2단계 페이지 테이블)

- Three level page table scheme(3단계 페이지 테이블)

- Hashed Page Table

- Inverted Page Table

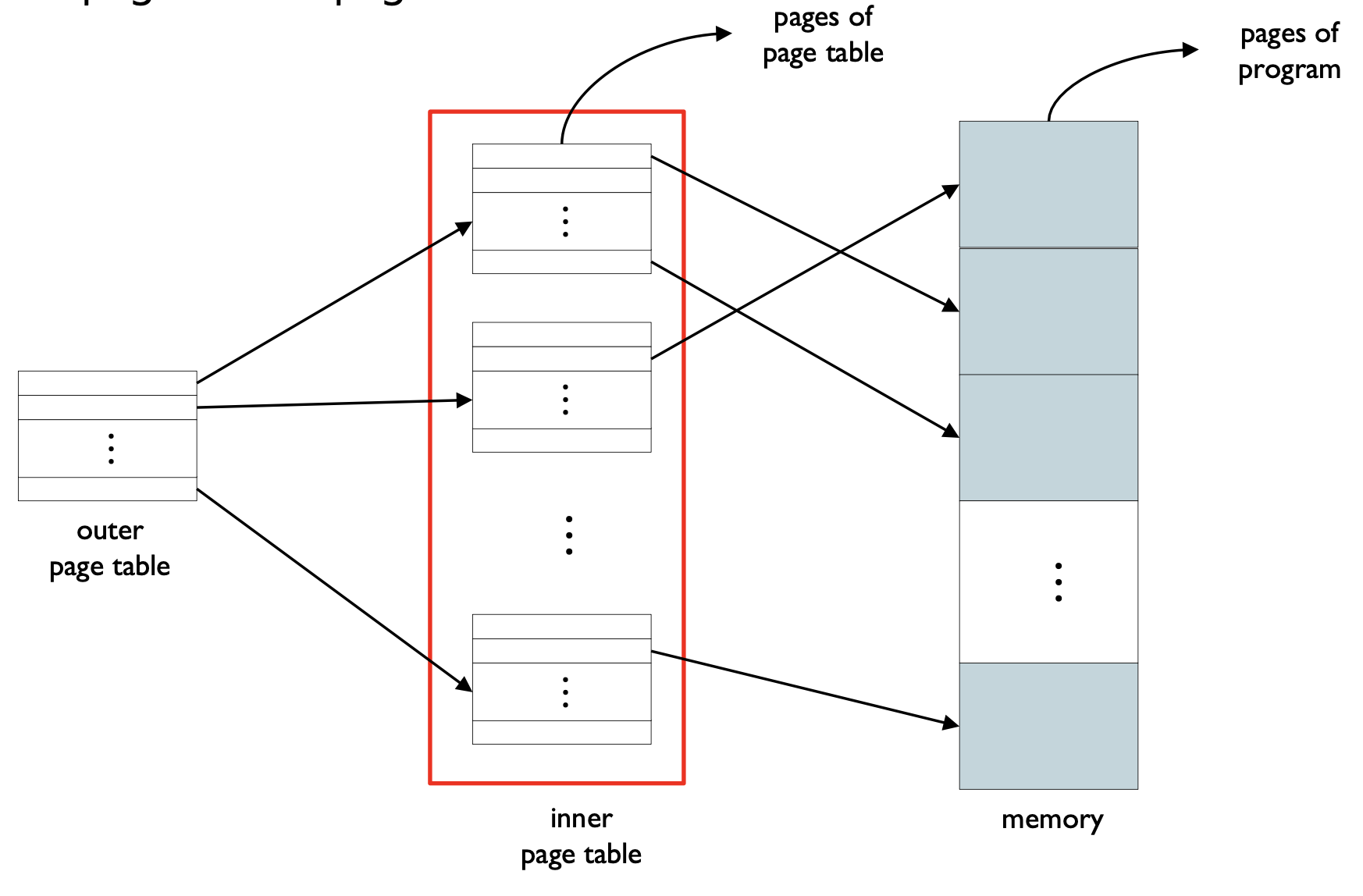

2단계 페이지 테이블

- 페이지 테이블 자체로 페이징된다

- 모든 페이지 테이블을 디스크에 저장한다

- 필요할 때 페이지 테이블의 페이지를 적재한다

페이지 테이블 공간 문제를 해결하기 위해 다양한 방법들이 제안되었습니다만, 가장 많이 사용되는 것이 다단계 페이징 기법입니다.

여기에서는 2단계 페이지 테이블 구조를 설명드리겠습니다.

그림의 가장 오른쪽에 메모리가 있고, 가운데에 페이지 테이블이 존재합니다.

이 기법의 핵심은, 페이지 테이블도 메모리에 적재되므로 페이지 테이블 자체를 페이징한다는 것입니다.

즉, 페이지 테이블 전체는 디스크에 저장해두고, 필요할 경우 하나씩 적재하는 방법이지요.

따라서, 페이지 테이블을 구성하는 각 페이지가 디스크 혹은 메모리에 있을 수 있으므로, 이러한 정보를 담고 있는 상위 레벨의 페이지 테이블이 하나 더 필요합니다.

물론 상위 레벨의 페이지 테이블은 항상 메모리에 있어야겠지요.

여기에서는 각각을 구분하기 위해 기존의 페이지 테이블을 내부 페이지 테이블(inner page table), 상위 레벨의 페이지 테이블을 외부 페이지 테이블(outer page table)이라 부르겠습니다.

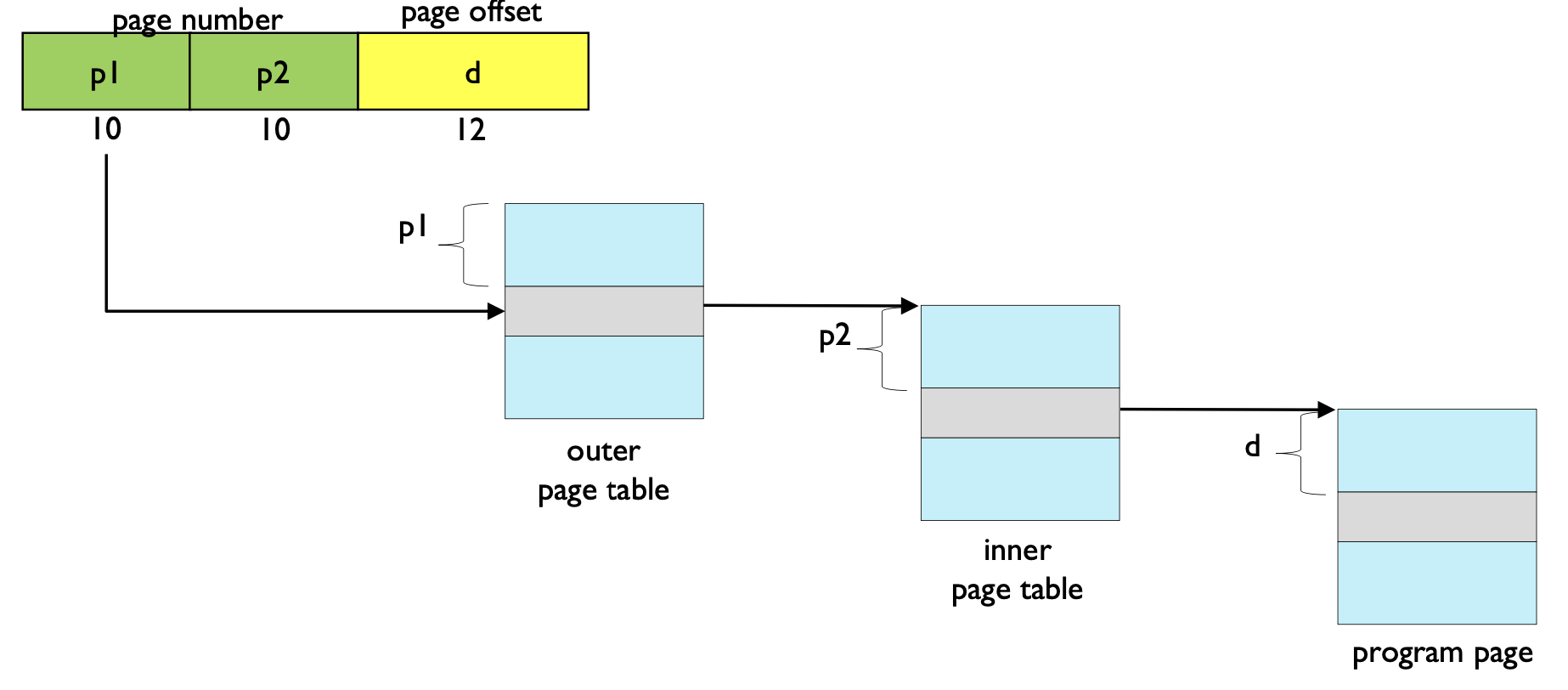

2단계 페이지 테이블 체계를 사용한 주소 변환

- 논리 주소(4K 페이지 크기의 32비트 주소)가 분할됩니다.

- 20비트 페이지 번호입니다.

- 12비트 페이지 오프셋입니다.

- 페이지 테이블 자체가 호출되기 때문에 페이지 번호가 더 분할됩니다.

- 외부 페이지 테이블의 인덱스는 10비트입니다.

- 내부 페이지 테이블의 인덱스는 10비트입니다.

3단계 페이지 테이블

64비트 프로세서의 3단계 페이징

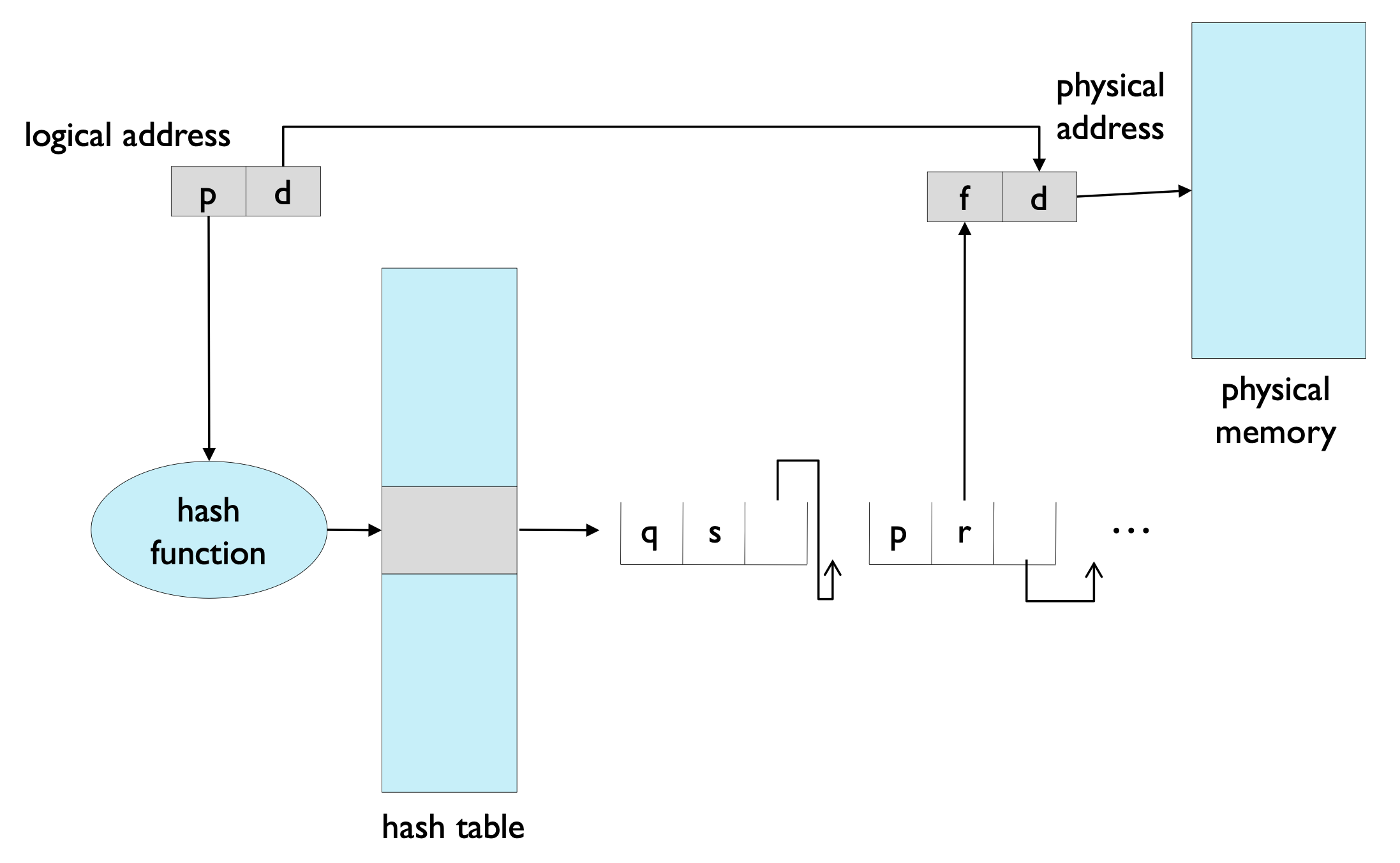

Hashed Page Table

- 논리 페이지 번호(logical page number)가 테이블에 해시된다

- 즉, Hash Table을 사용하여 논리 페이지 번호를 해싱한다.

- 해시 테이블은 동일한 위치에 해시된 요소들의 체인을 포함한다

- 논리 페이지 번호는 체인 내 항목(엔트리)들의 첫 번째 필드와 일치하는지 비교한다

- 만약 일치하는 항목이 발견된다면, 해당 물리 프레임 번호(physical frame number)를 얻는다

(논리 번호를 해시함수에 넣어 얻는 해시 값을 인덱스로 하여 일치하는 페이지 테이블 엔트리를 찾는다)

Inverted Page Table(역 페이지 테이블)

페이지 테이블의 공간 오버헤드

- 페이지 테이블 크기는 프로그램 크기에 비례합니다.

- 각 페이지(4KB)마다 하나의 페이지 테이블 엔트리(4B)가 필요합니다.

- 실제로는 한 번에 일부 페이지만 필요합니다.

역 페이지 테이블 (Inverted Page Table)

앞에서 봤던 페이징 구조에서는, 논리 주소를 물리 주소에 매핑하는 정보를 담는 페이지 테이블을 이용했다. 이 페이지 테이블은 현재 페이지(page number)가 어떤 프레임(base address)에 저장되있는지를 나타내고 있었다. 즉 page number를 base address로.

하지만 Inverted Page Table에서는 페이지 프레임을 기준으로 매핑 정보를 페이지 테이블에 저장한다. 각각의 프레임들이 어떤 프로세스의 어떤 페이지에 할당되어 있는가를 나타낸다. 따라서 프레임의 수와 페이지 테이블의 엔트리 수가 같다. 페이지 테이블의 i번째 엔트리는 physical memory의 i번째 프레임에 해당한다.

CPU가 pid와 page number를 알려주면, 몇 번째 프레임에 해당하는 지 알려주는 구조이다.

- 각 페이지 프레임마다 하나의 페이지 테이블 엔트리.

- 각 페이지 테이블 엔트리는 프로세스 ID를 포함해야 합니다.

- 시스템에는 하나의 페이지 테이블만 있으면 충분합니다.

- 엔트리는 페이지 프레임의 수만큼 필요합니다.

- 이는 연관 검색(associative search)이며, 전체 테이블을 검색해야 합니다.

- 페이지 테이블을 저장하는 데 필요한 메모리를 줄이지만, 테이블 검색에 필요한 시간이 증가합니다.

- 따라서 해시 테이블이나 연관 레지스터를 사용해야 합니다.

Inverted Page Table Diagram

역 페이지 테이블 구조도

(참고)

- CPU에서 논리 주소(logical address)를 생성합니다.

- 논리 주소는 PID, 페이지 번호(p), 변위(d)로 구성됩니다.

- 페이지 테이블을 검색하여 일치하는 항목을 찾습니다.

- 페이지 테이블 항목은 프로세스 ID(pid)와 페이지 번호(p)를 포함합니다.

- 물리적 주소(physical address)는 프레임 번호(i)와 변위(d)로 구성됩니다.

- 물리적 주소를 사용하여 실제 메모리에 접근합니다.

Segmentation

페이징 기법에서는 프로그램 이미지를 무조건 페이지라고 하는 고정된 크기로 잘라 메모리에 적재하였습니다.

이와는 달리, 프로그램 이미지를 세그먼트 단위로 적재하는 기법이 있는데, 이를 세그먼테이션이라고 합니다.

여기서 세그먼트란 프로그램 이미지를 구성하는 코드, 데이터, 스택, 힙, 심볼 테이블 등을 의미합니다.

즉, 프로그램을 단순히 바이트들의 배열로 보는 것이 아니라, 세그먼트들의 집합으로 이해하고, 이러한 단위로 메모리를 관리하자는 개념입니다.

세그멘테이션 (Segmentation)

- 프로그램은 여러 세그먼트의 집합입니다.

- (데이터, 힙, 스택, 코드 등 다양한 세그먼트로 구성됩니다.)

- (각 세그먼트는 물리 메모리에 개별적으로 배치됩니다.)

Segment Table

세그먼트 테이블

- 세그먼트 테이블은 프로그램 이미지 내에서 각 세그먼트의 위치를 나타냅니다.

- 예: 세그먼트 0, 세그먼트 1, 세그먼트 2, 세그먼트 3, 세그먼트 4.

논리 주소 구성 (Logical address consists of)

- 논리 주소는 <세그먼트 번호, 오프셋>으로 구성됩니다.

세그먼트 테이블

- 각 테이블 엔트리는 다음을 포함합니다.

- base: 세그먼트가 메모리에 위치한 시작 물리 주소.

- limit: 세그먼트의 길이.

세그먼트 테이블 베이스 레지스터 (Segment-table base register, STBR)

- 메모리 내 세그먼트 테이블의 위치를 가리킵니다.

세그먼트 테이블 길이 레지스터 (Segment-table length register, STLR)

- 프로그램에서 사용되는 세그먼트의 수를 나타냅니다.

- 세그먼트 번호 s는 s < STLR일 때 합법적입니다.

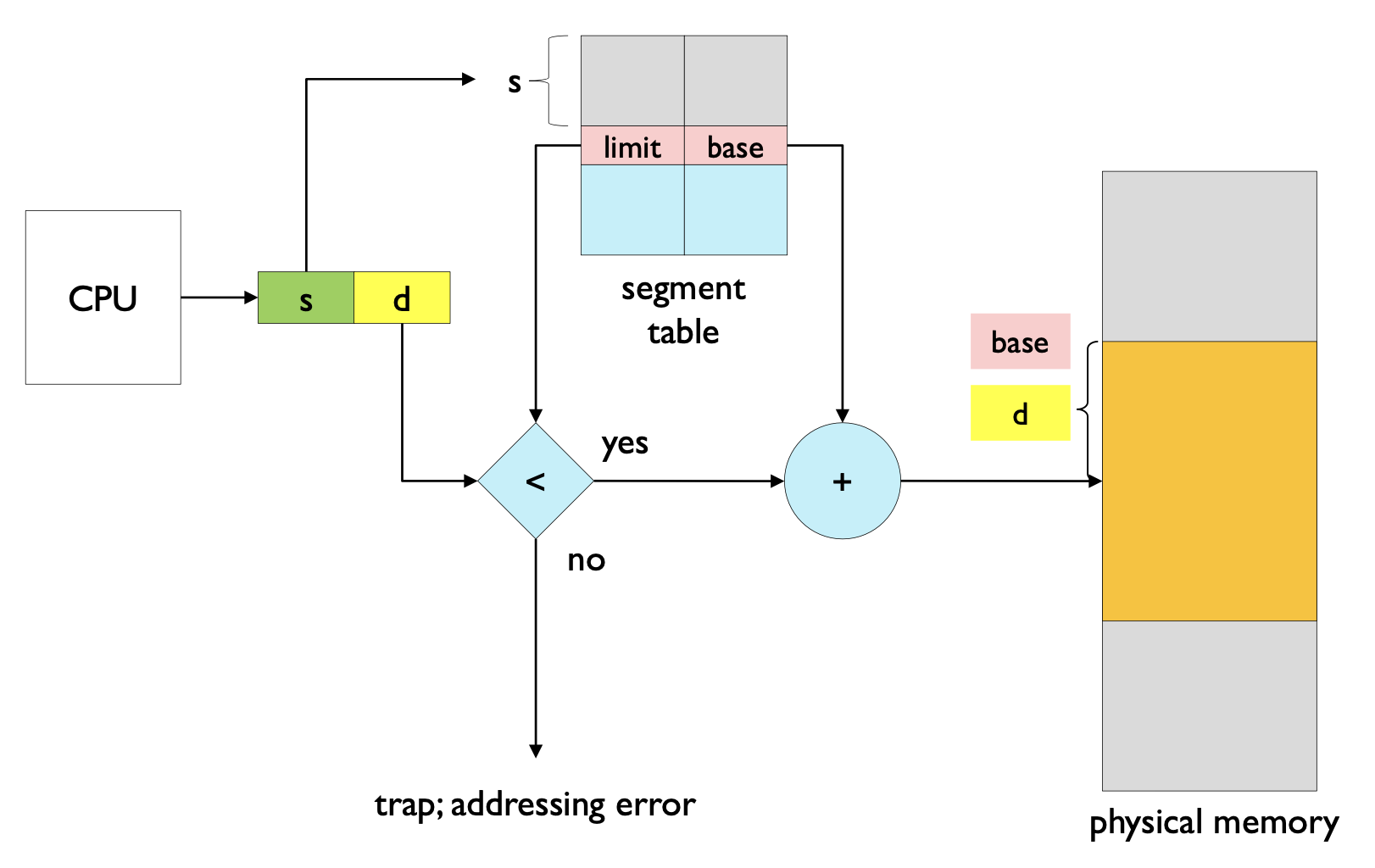

Address Translation with Segmentation Architecture

세그먼테이션 아키텍처를 사용한 주소 변환

세그먼트 테이블을 이용한 주소 변환 과정을 그림을 통해 설명드리겠습니다.

CPU가 요청한 논리주소 중 s로 표시된 상위 비트들은 세그먼트 테이블에서 인덱스로 사용되어, base 값을 통해 해당 세그먼트가 적재된 메모리의 시작주소를 알아냅니다.

논리주소 중 d로 표시된 하위 비트들은 limit 값을 통해 요청 주소가 해당 세그먼트의 범위를 넘지 않았는지 확인하고, 넘지 않았을 경우에는 base 값에 더해져서 물리주소로 변환됩니다. (위에서 봤던 limit register가 하는 역할과 비슷)

참고) 그림 설명

- CPU는 논리 주소를 생성합니다.

- 논리 주소는 세그먼트 번호(s)와 변위(오프셋)(d)로 구성됩니다.

- 세그먼트 테이블에서 세그먼트 번호(s)를 사용하여 베이스(base)와 리미트(limit)를 검색합니다.

- 변위(d)가 리미트(limit)보다 작으면 물리 주소가 계산됩니다.

- 베이스(base)와 변위(d)를 더하여 물리 주소를 생성합니다.

- 변위(d)가 리미트(limit)를 초과하면 주소 오류가 발생합니다.

Segmentation

보호 (Protection)

- 보호 비트(Protection bits)는 세그먼트와 연관됩니다.

- 유효성 비트(validation bit).

- 읽기/쓰기/실행 권한.

코드 공유 (Code sharing)

- 코드 공유는 세그먼트 단위에서 발생합니다.

세그먼트 길이가 다양하므로

- 동적 저장 할당 문제(dynamic storage-allocation problem)가 존재합니다.

- 첫 맞춤(first-fit), 최적 맞춤(best-fit), 최악 맞춤(worst-fit)을 기억하시나요?

Segmentation에서 "보호 비트를 사용할 수 있고, 코드 공유를 할 수 있고, 동적 저장 할당 문제가 존재한다" 정도 알고 넘어가자

'Computer Science > OS' 카테고리의 다른 글

| [운영체제] 11. Mass-Storage Structure (0) | 2024.06.19 |

|---|---|

| [운영체제] 10. Virtual Memory (0) | 2024.06.19 |

| [운영체제] 08. Deadlocks (0) | 2024.06.19 |

| [운영체제] 07. Synchronization Examples (0) | 2024.06.19 |

| [운영체제] 06. Synchronization Tools (0) | 2024.06.19 |